Northwest-AI-Hub at the 2026 Commons Annual Meeting

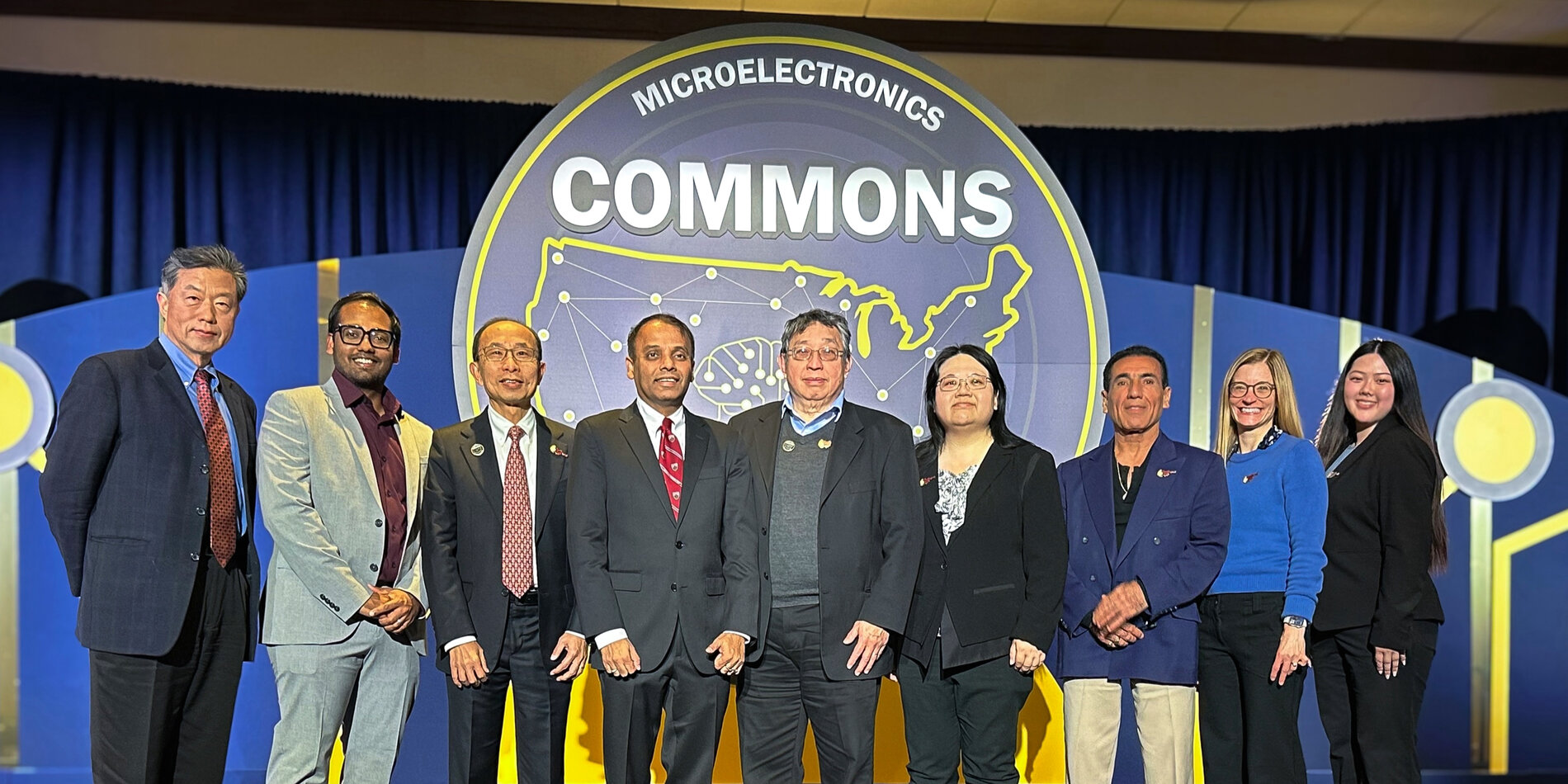

Representatives of the Northwest AI Hub at the 2026 Microelectronics Commons Annual Meeting in Washington, D.C.

Representatives from across the Microelectronics Commons ecosystem -- including all eight regional hubs, along with partners from government, industry, academia, and national laboratories -- gathered in Washington, D.C., for the 2026 Microelectronics Commons Annual Meeting, held February 17-20 at the JW Marriott. Members of the California-Pacific-Northwest AI Hardware Hub (Northwest AI Hub), led by Stanford University, joined the event to share updates on key technical and workforce development initiatives, connect with collaborators, and highlight ongoing efforts advancing AI-enabled microelectronics.

The annual gathering convened stakeholders from government, industry, academia, and national laboratories to share progress, exchange ideas, and strengthen collaboration across the Microelectronics Commons ecosystem. Throughout the week, keynote sessions, technical presentations, and workforce-focused programming highlighted the shared national goal of strengthening U.S. leadership in microelectronics and advanced manufacturing.

Prof. Philip Wong, Co-Chair of the Northwest AI Hub, presents an overview of the Hub and its CMOS+X Route (CXR) initiative at the 2026 Microelectronics Commons Annual Meeting.

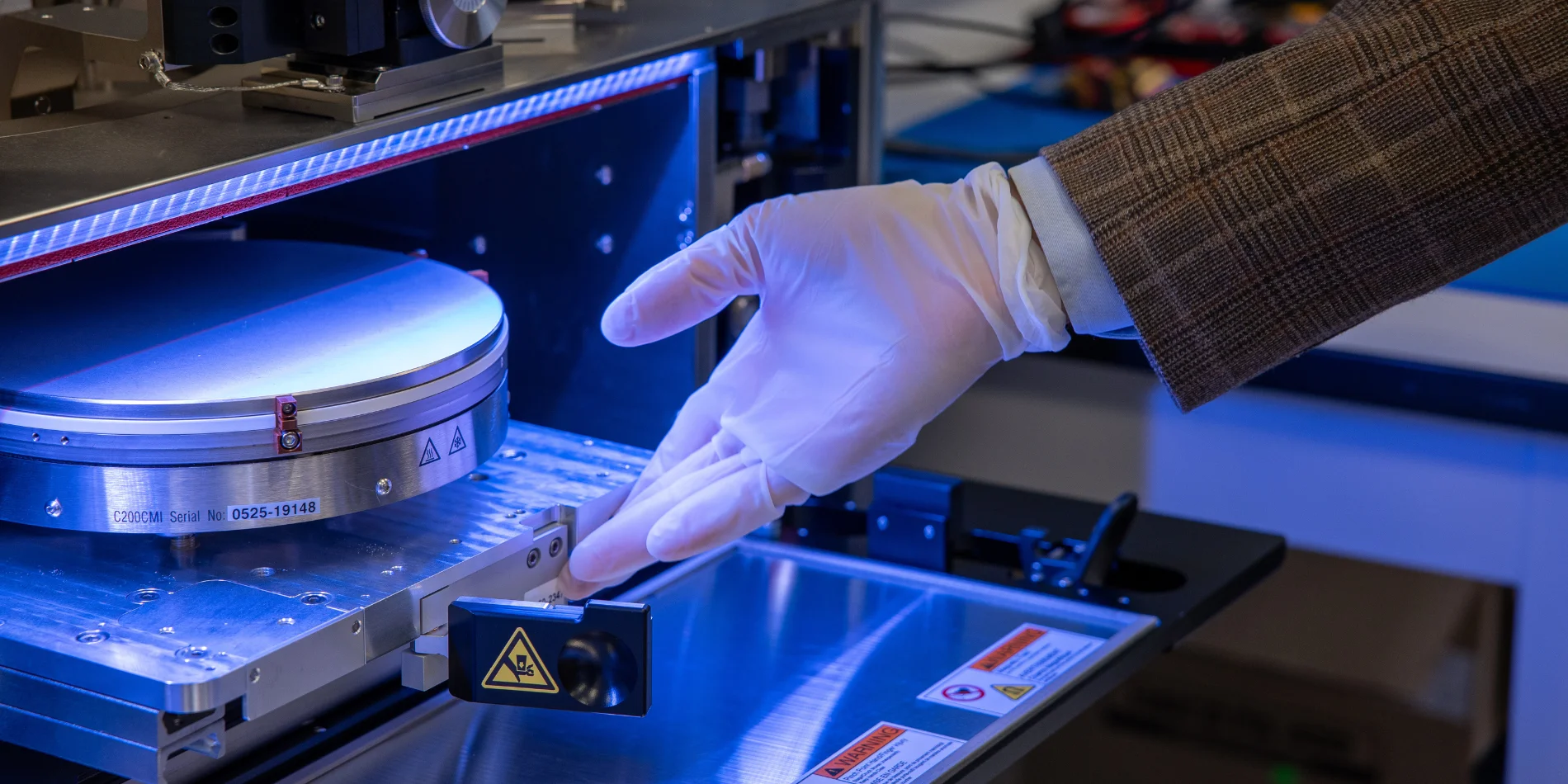

Advancing AI Hardware Innovation

During the meeting, Northwest AI Hub Co-Chair Philip Wong presented an overview of the Hub’s progress and highlighted its flagship initiative, CMOS+X Route (CXR). The program provides a scalable infrastructure model designed to expand secure, affordable access to advanced CMOS foundries while enabling novel “+X” integration approaches for emerging technologies.

A major milestone for the initiative is the CXR multi-project wafer (MPW) pilot shuttle, which brought together 16 users across startups, universities, industry, and a national laboratory. Taped out in January, the pilot aggregated 21 AI and secure-system designs onto a shared wafer, demonstrating the potential of collaborative fabrication infrastructure to accelerate early-stage hardware innovation.

The Hub also announced plans for its next CMOS+X MPW shuttle, which will utilize TSMC 28nm technology, with applications expected to open in Spring 2026. The program is designed to reduce barriers for researchers and startups while protecting intellectual property and enabling faster transitions from laboratory concepts to manufacturable hardware.

Dr. Sara Ostrowski, Associate Director of the Northwest AI Hub, shares updates on the Northwest AI Hub’s Workforce Development strategy during the Microelectronics Commons Annual Meeting.

Building the Workforce for Microelectronics

In addition to technical sessions, the meeting featured a dedicated Workforce Development (WFD) track, reflecting the importance of cultivating the talent pipeline needed to sustain long-term leadership in microelectronics.

Representing the Northwest AI Hub, Sara Ostrowski shared updates on the Hub’s workforce development strategy and progress across partner institutions. Meanwhile, Subhashish Mitra presented updates on ScaleAI, one of the Hub’s technical projects focused on enabling energy-efficient, scalable AI hardware through heterogeneous chiplet integration.

Together, these sessions underscored the dual priorities of advancing cutting-edge microelectronics technologies while building the workforce capable of designing, manufacturing, and scaling them.

Members of the Northwest AI Hub engage with attendees during the Hub Expo at the 2026 Microelectronics Commons Annual Meeting.

Engaging the Commons Community

One of the highlights of the week was the Hub Expo, which created opportunities for direct engagement across the Commons ecosystem. At the Northwest AI Hub booth, representatives connected with collaborators and attendees from across research, workforce, and commercialization initiatives, discussing ongoing projects and exploring new opportunities for partnership.

The Hub also highlighted the work of its workforce development partners at the University of California, Berkeley, who showcased a custom drone built on their RiskyBot open-source platform alongside student-designed silicon projects. The demonstrations illustrated a full silicon-to-systems pipeline, emphasizing the impact of hands-on microelectronics education and training.

A custom drone built on UC Berkeley’s RiskyBot open-source platform demonstrates hands-on microelectronics education and silicon-to-systems integration.

Strengthening the Commons Ecosystem

As the 2026 Microelectronics Commons Annual Meeting came to a close, the event underscored the critical role of collaboration across industry, government, and academia in advancing innovation and strengthening national capabilities in AI-enabled microelectronics.

We thank all participants for the engaging discussions and collaborations throughout the week, and recognize NSTXL (National Security Technology Accelerator) for its continued leadership in organizing the event.